# scientific reports

# **OPEN**

# A 64k pixel CMOS-DEPFET module for the soft X-rays DSSC imager operating at MHz-frame rates

Stefano Maffessanti<sup>1</sup>, Karsten Hansen<sup>1</sup>, Stefan Aschauer<sup>2</sup>, Andrea Castoldi<sup>1</sup>, Florian Erdinger<sup>5</sup>, Carlo Fiorini<sup>3,4</sup>, Peter Fischer<sup>6</sup>, Pradeep Kalavakuru<sup>1</sup>, Helmut Klär<sup>7</sup>, Massimo Manghisoni<sup>8,9</sup>, Christian Reckleben<sup>1</sup>, Lothar Strüder<sup>2,10</sup> & Matteo Porro<sup>7,11</sup>

The 64k pixel DEPFET module is the key sensitive component of the DEPFET Sensor with Signal Compression (DSSC), a large area 2D hybrid detector for capturing and measuring soft X-rays at the European XFEL. The final 1-megapixel camera has to detect photons with energies between 250 eV and 6 keV, and must provide a peak frame rate of 4.5 MHz to cope with the unique bunch structure of the European XFEL. This work summarizes the functionalities and properties of the first modules assembled with full-format CMOS-DEPFET arrays, featuring 512 x 128 hexagonally-shaped pixels with a side length of 136 µm. The pixel sensors utilize the DEPFET technology to realize an extremely low input capacitance for excellent energy resolution and, at the same time, an intrinsic capability of signal compression without any gain switching. Each pixel of the readout ASIC includes a DEPFET-bias current cancellation circuitry, a trapezoidal-shaping filter, a 9-bit ADC and a 800-word long digital memory. The trimming, calibration and final characterization were performed in a laboratory testbench at DESY. All detector features are assessed at 18 °C. An outstanding equivalent noise charge of 9.8e<sup>-</sup>rms is achieved at 1.1-MHz frame rate and gain of 26.8 Analog-to-Digital Unit per keV (ADU/keV). At 4.5 MHz and 3.1 ADU/keV, a noise of 25.5 e<sup>-</sup>rms and a dynamic range of 26 ke<sup>-</sup> are obtained. The highest dynamic range of 1.345 Me<sup>-</sup> is reached at 2.25 MHz and 1.6 ADU/keV. These values can fulfill the specification of the DSSC project.

The European XFEL (EuXFEL) is an X-ray Free Electron Laser source, where up to 2700 extremely brilliant X-ray pulses of a single bunch train at 4.5 MHz are repeated every 100 ms¹. Its unique bunch scheme poses big design challenges for the imaging detector development. Three 1-megapixel detector types have been specifically designed with different concepts to cope with the required X-ray energy range, peak frame rate and dynamic range.

The Large Pixel Detector  $(LPD)^2$  has square pixels of 500- $\mu$ m size, and was designed to be operated in the energy range between 5 and 20 keV. Its pixel electronics features a charge sensitive amplifier (CSA) with three gain stages and a 512-cell analogue memory per stage operated in parallel. The digitization is executed during the train gaps thanks to an on-chip column-level analog-to-digital converter (ADC). The convenient gain path is selected off-chip in order to achieve the maximum dynamic range. The detector is part of the Femtosecond X-ray Experiments (FXE) scientific instrument at EuXFEL<sup>3</sup>.

The Adaptive Gain Integrating Pixel Detector  $(AGIPD)^4$  targets the same energy range as the LPD, but offers a spatial resolution of 200  $\mu m$ . It features a CSA with three gains dynamically selected depending on the CSA output. A correlated double sampling (CDS) stage removes the reset noise, and its output is stored in a 352-cell analogue memory. Its analog data is subsequently digitized by off-chip ADCs. The AGIPD is part of the Single Particles, Clusters, and Biomolecules & Serial Femtosecond Crystallography (SPB/SFX)<sup>5</sup> and of the Materials Imaging and Dynamics (MID)<sup>6</sup> Instruments.

<sup>1</sup>Deutsches Elektronen-Synchrotron DESY, Notkestr. 85, 22607 Hamburg, Germany. <sup>2</sup>PNSensor GmbH, 81739 Munich, Germany. <sup>3</sup>Dipartimento di Elettronica, Informazione e Bioingegneria, Politecnico di Milano, 20133 Milan, Italy. <sup>5</sup>EXTOLL GmbH, 68159 Mannheim, Germany. <sup>6</sup>Institute for Computer Engineering (ZITI), Heidelberg University, 69120 Heidelberg, Germany. <sup>7</sup>European XFEL, Holzkoppel 4, 22869 Schenefeld, Germany. <sup>8</sup>Dipartimento di Ingegneria e Scienze Applicate, Università di Bergamo, 24044 Dalmine, Italy. <sup>9</sup>Istituto Nazionale di Fisica Nucleare, Sezione di Pavia, 27100 Pavia, Italy. <sup>10</sup>University of Siegen, 51228 Siegen, Germany. <sup>11</sup>Department of Molecular Sciences and Nanosystems, Ca' Foscari University of Venice, 30172 Venezia, Italy. <sup>∞</sup>email: stefano.maffessanti@desy.de

The Depleted Field Effect Transistor (DEPFET) Sensor with Signal Compression (DSSC) is targeting the soft X-ray range between 250 eV and 6 keV. A first camera is based on passive miniaturized silicon drift detector (mini-SDD) cells of hexagonal shape with a side length of 136 µm<sup>7</sup>, corresponding to an equal-area diameter of 247 µm. The readout chain of each pixel comprises a CSA, a time-variant filter with trapezoidal weighting function, a 9-bit ADC with gain-and offset-trimming capability, and a SRAM with a storage capacity of 800 samples. Therewith, the DSSC detector not only offers the deepest storage capacity among the three detector versions, but is also unique with its per-pixel digitizer approach. Another unique feature concerns the power-down capability of unused analog and mixed-signal blocks during memory readout within inter-train gaps. In this way, the in-vacuum power dissipation is drastically reduced to 149 W in contrast to the AGIPD (550 W). The power consumption of the 1-megapixel detector comprising the outside-vacuum electronics is 263 W compared to the AGIPD (1.2 kW<sup>4</sup>) and LPD (12 kW<sup>8</sup>). The gain of the signal processing chain can be adjusted in the CSA, in the filter and in the ADC, so that the current version of the DSSC imager with passive mini-SDD sensor covers the entire energy range with a gain granularity below one percent<sup>7</sup>. The imager reached an equivalent noise charge (ENC) of about 60 e<sup>-</sup> rms at the peak frame rate of 4.5 MHz, where the linear dynamic range is limited to maximal 9 bit. The camera was commissioned and is in use at the Spectroscopy and Coherent Scattering (SCS)<sup>9</sup> and Small Quantum Systems (SQS) soft X-ray instruments at EuXFEL.

Other detectors targeting the soft X-ray regime well below 1 keV are also based on the hybrid technology or originate from the class of charge-coupled devices (CCD) and monolithic CMOS imagers. They offer a higher spatial resolution but are limited in frame rates. To improve the performance at low X-ray energies, a novel CCD readout, called single electron sensitive readout (SiSeRO), is being developed at the MIT Lincoln Laboratory<sup>10</sup>. It features a floating gate amplifier composed by a MOSFET transistor with an internal gate used to read out the charge collected by the CCD matrix, and is based on the repetitive non-destructive readout (RNDR) DEPFET concept<sup>11</sup>. The authors of the paper could obtain a noise performance of 15 e<sup>-</sup>rms at 500 kpixel/s, corresponding to a frame rate of about 2 Hz of their readout concept. As hybrid candidate, the MÖNCH detector reached an ENC of about 40 e<sup>-</sup>rms at 3 kfps for a unique 25-µm pixel pitch<sup>12</sup>. The pnCCD detector with 75-µm pixel pitch is part of the SQS instrument at EuXFEL and can be operated up to 100-Hz frame rates. In user experiments, an ENC around 10 e<sup>-</sup>rms was achieved<sup>13</sup>. A monolithic example is the soft X-ray CMOS image sensor (sxCMOS), which is based on low-oxygen concentration Czochralski-grown silicon wafers and backside thinned to 45 μm. With a pixel pitch of 22.4 µm, the imager achieved 8.1 e<sup>-</sup>rms noise level at a speed of 450 Hz<sup>14</sup>. Except sxCMOS, all aforesaid cameras utilize thick high-resistivity wafer substrates for photon absorption, enabling their efficient use also at higher photon energies, whereas classical CMOS imagers make use of thin epitaxial layers. Recently, a sufficient quantum efficiency in soft X-ray domain was demonstrated for backside-illuminated imagers. Utilizing the 10 µm thick epi-layer of a commercial 180-nm CMOS technology and external post-processing of its backside, the 27-µm pixel pitch Percival detector obtained a maximum frame rate and minimum ENC of about 83 Hz and 16 e<sup>-</sup>rms, respectively<sup>15</sup>. Moreover, Desjardins et al. <sup>16</sup>, used a fully commercial CMOS imager (GSENSE 400BSI-GP) with 4-µm epi-layer and 11-µm pixel size for experiments at the soft X-ray branch of the metrologie beamline at SOLEIL synchrotron. They achieved a minimal ENC of 6 e<sup>-</sup>rms at a frame rate of 24 Hz. Fully-depleted CMOS imager approaches based on thinned and post-processed high-resistivity substrates also exist for soft X-ray applications <sup>17,18</sup>. In order to comply with the targeted high sensitivity and frame rate, the pixel electronics of the 50-µm pixel pitch ePixM detector is limited to nine transistors, and the digitization is shifted to a bump-bonded ADC tier. They strive for a frame rate and noise of 24 kHz and 11 e<sup>-</sup>rms, respectively.

The second DSSC camera addresses the challenge of low noise at high frame rates and is currently under construction. The new camera utilizes DEPFET pixel arrays in a fully customized double-sided 350-nm 2-poly 3-metal high-voltage CMOS process<sup>19</sup>. This active pixel sensor is based on 725 µm thick high-resistivity Si wafers extending not only the quantum efficiency far beyond the soft X-ray regime but also acting as radiation shield for the electronics layers behind the fully depleted Si bulk. The sensor combines an extremely low input capacitance for excellent energy resolution with an intrinsic capability of signal compression without any gain switching procedures in the analog front end. Signal charges are collected on an embedded internal gate implantation located underneath the DEPFET gate of the transistor for drain-current modulation. Its doping profile and shape causes the required non-linear response and extends the dynamic range maintaining the required singlephoton resolution in the linear gain region. Other benefits of the DEPFET approach concern its capability of pixel-size shrinkage below 30 μm<sup>19</sup> and of non-destructive readout to reach sub-electron noise performance<sup>11</sup>. These features underline the flexibility and future potential of this detector concept. An overview of the DEPFET devices development is detailed by Andricek et al.<sup>20</sup> The authors present the DEPFET applications dividing the device types in two subgroups: standard devices, used in high energy physics experiments and astrophysics, and non-standard devices. An example of the latter are the DEPFET with signal compression used in transmission electron microscopy and the RNDR recently proposed for the search of dark matter.

This work summarizes the functionalities and properties of the DSSC prototype modules, equipped with full-format CMOS-DEPFET sensors, for the first time. In "Camera and methods" section, a summary on the main building blocks of the camera-head electronics is given. We describe the trimming-relevant functionalities of the front-end electronics and introduce the experimental methods for performance verification. The "Results" section presents the laboratory test results of the individual key parameters measured at DESY. In particular, the sensor-pixel leakage current, the DEPFET-quiescent current, the electronics channel gain and offset in the primary linear gain region, the gain compression, and the total noise will be treated. The appraisal of the obtained results and comparison to other detectors are carried out in "Discussion and perspective" section.

#### Camera and methods

Camera head and periphery. The ladder camera operates a matrix of  $512 \times 128$  DEPFET pixels and represents the smallest independent building block of the megapixel camera. Therefore, we expect that the obtained results from the ladder prototypes are also representative for the full camera. Except for some DEPFET-related functions, the whole electronics shares the same design of the mini-SDD camera version. For a more detailed summary, we refer the readers to the mini-SDD review. In-depth descriptions on individual functions of all sub-assemblies can be found in the corresponding citations mentioned below.

The ladder camera consists of a focal-plane module (FPM), four regulator boards (RB), a central I/O board (IOB), and a module-interconnection board (MIB). The FPM consists of a metal frame, main board, heat spreader, and sixteen application-specific integrated circuits (ASIC) mounted on two CMOS-DEPFET sensors<sup>21</sup>. Its main board distributes the ASIC- and sensor-related supply voltages as well as their clock and control signals. The RBs provide the permanent and cycled supplies for the ASICs and main board<sup>22</sup>. On-board gate drivers (GD) generate pulses to remove the signal charges collected by the internal gates of the DEPFET matrix. The IOB concentrates the data of the ASICs to four 3.125-Gbit/s links, controls the RBs, and provides the cycling of the DEPFET source and gate voltages<sup>23</sup>. The MIB provides the control signals for the GDs by on-board module amplifiers (MA)<sup>22</sup>, and collects all power supply, clock and data channels. A single flex cable connects the ladder electronics to the peripheral patch-panel electronics, which is located outside the vacuum chamber. Its mother board represents the interface to external power supplies, and hosts the patch-panel transceiver (PPT) and safety-interlock board (SIB). The PPT reads the data streams of four IOBs (in our setup only a single ladder is connected), concentrates them in a suitable data format to four optical 10 Gigabit-Ethernet links, and supports a machine-synchronized operation of the detector<sup>23</sup>. The SIB protects the detector by identifying anomalies and probable hazardous situations in the vacuum chamber and power crates<sup>24</sup>.

**Signal processing.** The FPM is equipped with two monolithic  $256 \times 128$  DEPFET pixels sensors. Each sensor is divided in eight electrically independent octants, composed of  $64 \times 64$  pixels, that share the single entrance window on the sensor backside. The DEPFET is biased in a common source configuration, and thus the DEPFET source and gate contacts are shared octant-wise, whereas their drain contacts are pixel-wise bump-bond connected to the signal-processing chain of the readout ASIC.

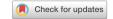

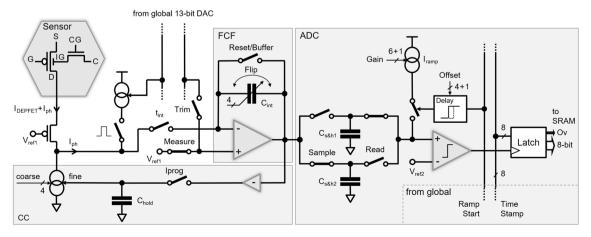

Figure 1 shows a simplified block diagram of the pixel-level electronics. The front-end circuitry consists of a cascode stage to fix the DEPFET's drain voltage and a programmable current source (4 bit coarse) to sink the DEPFET quiescent current I<sub>DEPFET</sub>. The fine regulation of the current-compensation (CC) circuit is obtained through an additional analog branch consisting of a capacitor (Chold) and a switch (Iprog) connecting the output of the flipped-capacitor filter (FCF)<sup>25</sup>. CC is automatically tuned prior to the arrival of an X-ray bunch train (zero signal). The time-variant filter implements a trapezoidal weighting function and performs an optimal noise filtering at the foreseen readout speed. Its key timing parameters are programmable in 1.44-ns time steps, and four feedback capacitors (C<sub>int</sub>) provide the coarse-gain flexibility to cope with different experimental requirements. The timing diagram for the two operating modes are described in Fig. 2a. In normal operation (normal op.), the filter integrates the DEPFET current twice. In the first phase (1st tint) it integrates the residual bias-current (baseline (BL) measurement), and in the second phase (2nd  $t_{int}$ ) it integrates the DEPFET-signal current (BL + signal measurement). Since the feedback capacitance is flipped between the first and the second integration (Cint flip), the output of the filter at the end of the second phase is already a measurement of the baseline-subtracted signal. Thanks to its flexibility, the filter can also be programmed in order to integrate only the signal current at the expenses of the BL subtraction (single int.). In any case, the duration of the signal-current integration is controlled by the switch  $t_{int}$ . As illustrated in Fig. 1, two sample and hold capacitors  $(C_{s\&h1.2})$  are operated in a double-buffer fashion (alternating sample & read) at the output of the filter. A single-slope Wilkinson-type 9-bit ADC performs the analog-to-digital conversion  $^{26}$ . The voltage on  $C_{s\&h}$  is ramped with a programmable current source  $I_{ramp}$  (6 bit fine plus double-current bit). The time required for the ramp to reach a reference voltage ( $V_{ref2}$ ) is measured. The 8-bit Gray-coded time stamps are provided column-wise at about 695 MHz, providing a bin size

Figure 1. Simplified block diagram of the pixel-level electronics.

**Figure 2.** Simplified timing diagram of a single acquisition cycle (**a**) showing the normal and the single integration modes. Special modes in single integration (**b**) are used for the leakage current and the non-linear response characterization.

of 720 ps (dual-edge clocking). The ninth bit (Ov) is generated in-pixel to save routing area. The programmable ramp current allows a fine-tuning of the ADC gain with a resolution of about 2%. Additionally, the ADC provides an offset trimming by adjusting the delay between the start of the counter (Ramp Start) and current injection on  $C_{s\&h1,2}$ . The 4-bit controllable delay circuit allows an offset granularity better than 10% of the ADC-bin size. Both trimming capabilities are needed to minimize the pixel-error rate at and below the sensitivity level of one photon per bin 7.26. For test, trimming and calibration purposes, a global 13-bit digital-to-analog converter (DAC) is available on-chip. The programmable voltage is either provided to a pixel-internal current mirror for pulsed current injection at the negative input of the FCF during measurement (Measure) or provided to its positive input for ADC trimming (Trim) during FCF-buffer mode operation (Reset/Buffer).

A special timing sequence has been defined in order to measure the leakage current flowing into each pixel and to exploit the non-linear response characteristics of the DEPFET device (cf. Fig. 2b). The FCF is set to single integration mode, and the DEPFET internal gate (IG) is cleared only at the beginning of the train. In this way, the collected charge is integrated in the IG over several acquisition cycles and sampled. By means of a pulsed light source synchronized to the system, moreover, it is possible to increase the injected charge every cycle to scan the response of the DEPFET over several acquisition cycles thus relaxing the power constraints of the light source.

**Experimental setup.** The ladder camera head was hosted in a vacuum chamber operated at a pressure of  $5 \times 10^{-2}$  mbar. A Peltier-based cooling system was designed to cope with the in-vacuum power dissipation of the DEPFET ladder resulted up to 18.6 W, which corresponds, for the 1-megapixel detector, to 298 W in-vacuum and 412 W considering the outside-vacuum electronics. For comparison, the mini-SDD figures are  $9.3 \, \text{W}^7$ , 149 W and 263 W, respectively. The difference in the power dissipation is mainly due to the additional DEPFET-clear electronics (MA and GD) as well as the DEPFET-quiescent current. In the experiments presented here, the cooler kept the sensor temperature constant at around  $18\,^{\circ}\text{C}$  to avoid any overheating of the system and to ensure the thermal stability. A flange with a Kapton window was placed in front of the FPM in order to use a radioactive  $^{55}\text{Fe}$  source outside the vacuum chamber for pixel-wise energy calibration in the linear gain range, or to use an external pulsed laser diode (octant-wise illumination with 100 ns long pulses at 940-nm emission wavelength) for gain determination in the non-linear range. In both cases, the distance between source and the sensor backside was about 5 cm. Note, that the sensors' entrance window has a 150 nm thick light-blocking Al filter requested by the SQS instrument, which might be easily reduced to 30 nm (mini-SDD camera) increasing the quantum efficiency at low energies. A picture of the vacuum setup is shown in Fig. 3.

In all measurements, the power-cycling mode was used with 600  $\mu s$  long active time at a repetition rate of 10 Hz. The ladder was predominantly operated at a frame rate of 2.25 MHz. This operating speed relaxes the operation-critical time gaps between the clear/reset pulses and integration cycle (cf. Fig. 2a: "critical"). In this way, an optimization of levels and timing of source (S), gate (G), clear (C) and clear gate (CG) voltages was possible (Fig. 1). After optimization, the 4.5-MHz and 1.125-MHz modes were successfully operated. An integration time  $t_{int}$  = 50 ns and a clear-pulse width of 50 ns was used. The clear and clear-gate low levels (7.5 V & 4.5 V) as well as the source and gate voltages (5 V &  $\sim$  2.5 V) are switched on 16  $\mu s$  prior to the start of a bunch train and switched off at its end. The clear and clear-gate high levels (20.5 V & 11 V) are pulsed after each single bunch to clear the collected charge between two acquisition cycles. The IOB controls the operation-critical delay (7.5 ns & 5 ns) and width (50 ns & 37.5 ns) of the two signals independently. A corresponding timing configuration for 4.5-MHz frame rate was also prepared ( $t_{int}$  = 30 ns) and tested after optimization. In order to test the noise performance at lower frame rates, a 1.125-MHz sequence with  $t_{int}$  = 300 ns was exploited at different  $C_{int}$ .

**Figure 3.** View of the lab-vacuum chamber and particular of a CMOS-DEPFET ladder during the measurement campaign.

## **Results**

**DEPFET current.** The first operation that must be performed after switching on the sensor is to trim the coarse section of the CC circuit in order to minimize the  $I_{DEPFET}$  amount flowing to the FCF. This is done by choosing the coarse setting that allows a voltage on  $C_{hold}$ , called  $V_{hold}$ , maximizing the dynamic range of the analog branch. To achieve this, the in-pixel ADC is used to measure  $V_{hold}$  before the start of the bunch train at the end of the Iprog phase. Therefore, the ADC gain was beforehand equalized to uniform the response of all the pixels.

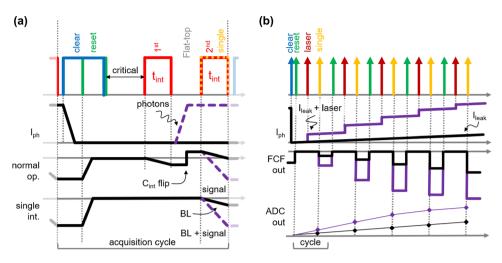

The  $I_{DEPFET}$  amount flowing into each pixel can be estimated by the knowledge of the CC-coarse setting and the measured  $V_{hold}$  thanks to the CC-circuit level simulations of the transfer characteristics. Figure 4a shows the map of the DEPFET-quiescent current for a gate voltage of 2.5 V. The electronics and power supply allow to adjust the source and gate voltages independently for the two sensors of the FPM, thus enabling the possibility of adjusting the average sensor-drain currents to obtain a uniform response over the focal plane. This is an important step to also equalize the DEPFET gain in the linear region being proportional to  $\sqrt{I_{DEPFET}}^{27}$ . For this purpose, the CC was trimmed, and the average per-pixel current was computed for three different gate voltages  $(V_G)$ . The transfer characteristics  $(I_{DEPFET}$  vs.  $V_G)$  allows to find the gate voltages to obtain the desired working point of  $100\,\mu\text{A/pixel}$ . The finally chosen gate voltages were 2.4 V and 2.71 V corresponding to an average  $I_{DEPFET}$  of  $99\,\mu\text{A}$  and  $101\,\mu\text{A}$  for sensor 1 and sensor 2, respectively. The source voltage was kept fixed at 5 V. The map of the current distribution after equalization, as well as the distribution comparison with the initial biasing condition are shown in Fig. 4b,c. A total number of 89 pixels (0.14%) were excluded from the average computation due to the high leakage currents or defects that prevents the proper operation of the CC circuit. These include the pixels of the two partial columns of sensor 1, where a defect in the middle of the column prevent the operation of the downstream pixels.

Figure 4. (a) DEPFET-quiescent current map of the ladder  $(512 \times 128 \text{ pixels})$  when both sensor gates are biased at 2.5 V. The ticks mark the sensor's octant separation (64 pixels). Sensor 1 (left) shows an average current slightly below the target value of 100  $\mu$ A, while sensor 2 (right) current is more than 10% higher. (b) Currents after the equalization. (c)  $I_{DEPFET}$  distributions before (blue) and after (magenta) the equalization.

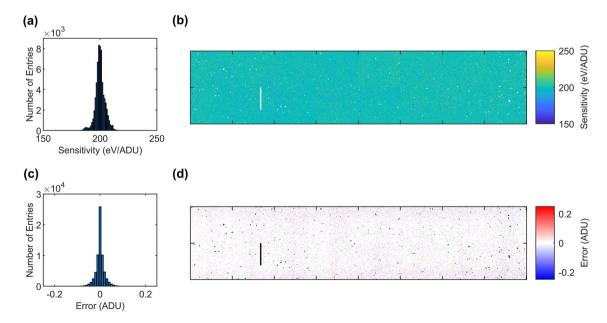

Pixel gain and offset. After equalization of the average quiescent current, the global gain of the system was assessed. An 55Fe-radioactive source (650 MBq) was used to irradiate one sensor at a time, achieving an average photon flux on the sensor of about 1.53  $\times$  10<sup>-4</sup> photon/pixel/frame, which corresponds to 281 photon/pixel/s. The radioactive source is an asynchronous source, and therefore the flat-top of the filter weighting function was extended to 500 ns in order to ensure a proper peak-to-shelf ratio in the acquired spectrum ( $t_{int} = 50$  ns). This timing variation is not altering the system gain, but increases the effective acquisition-cycle length, and therefore the number of acquirable frames was reduced accordingly to avoid exceeding the electronics power within the active time of 600 µs. The other timing delays were not changed with respect to the original 2.25-MHz configuration. The lowest C<sub>int</sub> of the FCF was selected in order to obtain the maximum coarse gain at the given integration time, and the ADC was previously trimmed to its nominal gain. A total of more than 13,000 trains of 400 frames each were acquired, and the histogram data for each pixel extracted. The single pixel spectra were fitted with a simplified fitting function derived from the work of Schlee<sup>28</sup>. In particular, the pedestal peak was fitted with a simple Gaussian function, while the Mn  $K_{\alpha}$  and  $K_{\beta}$  peak fit comprise a Gaussian function for the peaks and a shelf function to reduce the fit error on the peak position. The resulting average untrimmed gain was  $5.07 \, \mathrm{ADU/keV} \pm 3.62\%$  corresponding to a sensitivity of 197 eV/ADU. As the ADC was previously trimmed, the dispersion is mainly caused by the pixel-to-pixel variation in the FCF as well as by process variations in the sensor production.

To assess the system-trimming capabilities, an offline-gain trimming was performed with a target gain of 5 ADU/ keV. The ADC gain was measured pixel wise using the in-pixel current injection circuit, and a look-up table of the ADC gain was generated. Then, the gain ratio obtained from the look-up table was used to cross-calibrate each ADC gain, knowing the absolute gain from the radioactive source measurement. Finally, the nearest cross-calibrated ADC gain setting was selected and applied to the FPM. For verification, a new spectrum acquisition was taken and analyzed with the same method described before. A final gain of 5.00 ADU/ keV  $\pm$  2.09% was obtained that correspond to a sensitivity of 200 eV/ ADU, well in line with the expectation and trimming capabilities of the ADC. Less than 400 pixels (0.6%) were excluded from the analysis. These include mainly high-leakage pixels and pixels that show a low sensitivity. A map and a histogram of the sensitivity after trimming are shown in Fig. 5a,b. The ADC-offset trimming capability was also evaluated. For each offset step, a dark acquisition was performed and the pedestal peak fitted. The error with respect to the bin center was computed and the final offset setting chosen as the setting with the minimum offset error. As illustrated in Fig. 5c,d, all pixel offsets were found in the  $\pm 0.1~\rm ADU$  range with a dispersion of 0.02 ADU. 0.5% of the pixels showed instabilities, which corresponds to the pixels where the gain determination was not possible. These were excluded from the computation.

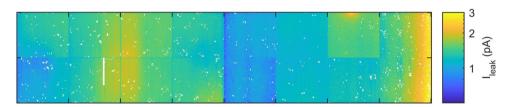

**DEPFET-leakage current.** In the next step, the pixel-leakage current was measured. The special timing sequence described in "Camera and methods" section (cf. Fig. 2b) was used to measure the leakage-induced charge within the time span of 400 frames. 1000 acquired trains were averaged frame by frame, and the resulting ramp was fitted with a linear regression model. Taking the system timing and the calibration into consideration, the leakage current of each pixel was computed by

$$I_{leak,px} = \frac{\Delta Q}{\Delta T} = \frac{\Delta N}{\Delta T} \cdot e = \frac{S}{G \cdot E_{e-h}} \cdot e,$$

**Figure 5.** Sensitivity distribution (**a**) and map (**b**) of the system after the offline trimming targeting 200 eV/ ADU. Offset error distribution (**c**) and map (**d**) after trimming.

where S[ADU/s] is the slope, G[ADU/eV] the pixel gain,  $E_{e-h} = 3.6 \, \text{eV}$  the energy to create an electron-hole pair in Si, and e the electron charge. The average leakage current per pixel was 1.35 pA corresponding to a current density of  $2.8 \, \text{nA/cm}^2$ . The leakage current map is shown in Fig. 6. Altogether, less than 950 pixels (1.4%) were excluded from the analysis mainly due to the missing gain information or measurement problems caused by the leakage current being too high.

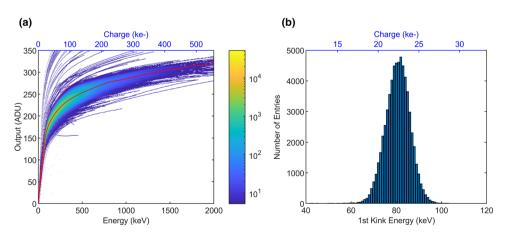

**Gain compression.** In another experiment, the non-linear response characteristics was measured in 9-bit ADC mode. Four hundred consecutive 100 ns-long laser pulses were used to generate a signal charge in the pixels internal gate. For this purpose, the leakage current measurement timing scheme was used again (cf. Fig. 2b). The integrated charge was measured at a gain suitable to explore the nonlinear characteristics. Therefore, a new  $^{55}$ Fe spectrum was acquired at the same gain condition to cross-calibrate the injected charge for each pixel, resulting in a sensitivity of  $473 \pm 22$  eV/ ADU. The superposition of the response characteristics of 63,498 pixels (96.9%), as well as the resulting average curve is shown in Fig. 7a. The outliers contain high-leakage pixels, calibration-failed pixels, and pixels with insufficient illumination level. From the average curve it is possible to calculate the gain compression as the ratio between the slope in the linear range versus the slope for energies above 1.5 MeV resulting in a compression ratio of 73.7. Furthermore, it is possible to estimate the dynamic range (DR) by extrapolating the average response curve above the maximum measured value. Taking the gain and saturation levels of the front-end electronics into account, the average DR is 2.13 MeV corresponding to 591 ke $^-$  or 4500 photons of an energy of 473 eV at one photon per bin resolution.

The minimum of the 2nd derivative of the response characteristics represents the position of the first DEPFET gain change (1st kink). It was computed and an average kink energy of  $80.61 \pm 5.44 \,\mathrm{keV}$  was found. Figure 7b displays the dispersion of the 1st kink energy.

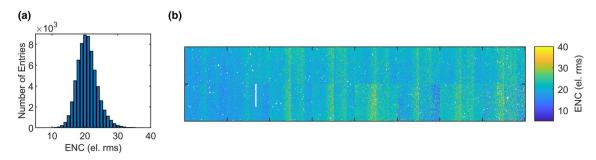

**Equivalent noise charge.** Finally, the ENC was measured in the same gain configuration as for the previous measurements but without the increased flat-top time used for the  $^{55}$ Fe measurement (flat-top time 43.2 ns). Thanks to the offset-trimming capabilities of the system, we used an ADC-bin edge as a knife edge to measure the pedestal width. First, the pixel-offset step size was determined using the method described by Hansen et al.  $^{26}$ . For all possible 16 offset steps, a ramp was generated, and a signal was acquired using the DEPFET-leakage current following the same technique as for its measurement. The 16 ramps were fitted with a linear regression. The slope of the subsequent linear regression of the intercepts versus the offset setting determines the offset average step size of  $133.8 \pm 21.3$  ps. The pedestal width was then measured acquiring a dark run of 250 trains for each offset setting. The number of counts above a reference ADC bin were extracted, and the resulting cumulative distribution function was fitted to extract the pedestal width. The ENC was then computed taking the calibrated

**Figure 6.** DEPFET-leakage current map showing an average leakage current per pixel of 1.35 pA at room temperature.

Figure 7. (a) Superposition of DEPFET characteristics with the average characteristic (red curve)  $\pm 3\sigma$  (dashed curves). (b) shows the distribution of energy position of the 1st kink in the non-linear response characteristics.

gain of  $5.00\,\mathrm{ADU/keV}$  into account. At an integration time of  $50\,\mathrm{ns}$ , an average ENC of  $20.7\pm3.1\,\mathrm{e^-rms}$  was measured. Figure 8 shows the histogram and map of the noise.

**Spectral performance and dynamic range.** During the above-mentioned test campaign using the first prototype ladder, a second ladder was tested to confirm the results obtained with the first prototype and to further investigate the noise and dynamic range performances of the system at different ASIC operating conditions. The DEPFET bias voltages and timing were kept fixed, as well as the target quiescent current of 100 µA. For each operating frequency, a spectrum acquisition and noise analysis have been conducted using the same methods as described above for the first prototype. In addition, the DR for each pixel was extrapolated. The DR determination method for the DSSC imager is described by Porro<sup>29</sup>. First, the ASIC DR was determined by subtracting the saturation level of each pixel from the pedestal centroid position. Then, the non-linear response, that is independent of the ASIC gain configuration, was taken into account. Due to the lack of data at high injection levels for all the ladder pixels, the average characteristics on the 165 pixels showing injection up to 1.5 MeV was used. In order to cover the required energy range to reach the ASIC saturation, the response was extrapolated by means of a linear regression of the last 100 keV to reach the saturation limit of the ASIC.

In a first experiment, the same conditions of the first ladder under test were applied. At the operating frequency of 2.25 MHz and an integration time of 50 ns, the same low noise performance was obtained. For the trimmed and calibrated gain of 5.05 ADU/keV  $\pm$  2.2% the resulting ENC was 18.5  $\pm$  2.7 e<sup>-</sup>rms. The average DR was 19 ke<sup>-</sup>. The same analysis was performed at two lower gain settings by increasing  $C_{\rm int}$  of the FCF, but skipping the gain trimming. At a gain of 2.2 ADU/keV  $\pm$  4.4% and 1.63 ADU/keV  $\pm$  5.3%, an ENC of 26.6  $\pm$  6.4 e<sup>-</sup>rms and 34.4  $\pm$  9.5 e<sup>-</sup>rms, and a DR of 489 ke<sup>-</sup> and 1.345 Me<sup>-</sup> can be obtained, respectively.

Another frequency of interest for the system is 1.125 MHz that corresponds to the maximum bunch-pattern frequency currently used in the mini-SDD camera experiments. This represents also the maximum bunch frequency foreseen in the next EuXFEL continuous wave upgrade in the so-called long-pulse mode<sup>30</sup>. This mode allows to increase the integration time up to 300 ns for the best noise performances of the DSSC. In two experiments, the FCF feedback capacitor value was changed in order to explore the performance at the low gain, for highest DR, and at high gain, for best noise performance. The lowest gain obtained was 2.5 ADU/keV  $\pm$  5.5% and an ENC of 20.14  $\pm$  5.6 e $^-$ rms. At high gain mode, we reached 13.4 ADU/keV  $\pm$  2.2% and an ENC of 10.5  $\pm$  2.1 e $^-$ rms. The DR were 165 ke $^-$  and 7 ke $^-$  at low and high gain, respectively.

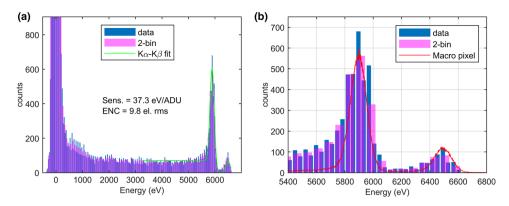

To explore the spectroscopic capabilities of the system, we further increased the overall gain near to the limits of the system by doubling the ADC gain, but keeping margin for the fine gain trimming. A final gain of 26.8 ADU/keV  $\pm$  2.5% was leading to the best noise performance of 9.8  $\pm$  1.4 e $^-$ rms. Figure 9 shows a representative  $^{55}$ Fe spectrum of a sample pixel. For comparison a spectrum of a macro pixel from an early development stage sample of the CMOS-DEPFET fabrication, a single DEPFET structure surrounded by SDD-type drift rings, is shown. The measurement was performed at  $-50\,^{\circ}$ C and 3- $\mu$ s shaping timel  $^{9}$ . A re-binned histogram, where two bins are merged in order to mitigate the DNL effects  $^{31}$ , is also displayed (cf. 2-bin). The DNL is mainly caused by the duty-cycle spread in the time-stamp distribution over the matrix. The average DR in this configuration is 5 ke $^-$ . Finally, we evaluated the performance at the maximum operating frequency of 4.5 MHz. This operating frequency is crucial for the timing sequence and does not allow any freedom in the choice of the parameters. In particular, an integration time of 30 ns was used in order to keep the DEPFET-timing scheme unchanged. The ADC gain was kept fixed, but the change in the integration time reduced the front-end gain by about 40%. An average gain of 3.12 ADU/keV  $\pm$  3.65% was finally obtained, and the ENC analysis reports a noise of 25.5  $\pm$  5.3 e $^-$ rms confirming the simulated performances of the system. The estimated average DR was 26 ke $^-$ . All the results are summarized in Table 1.

#### Discussion and perspective

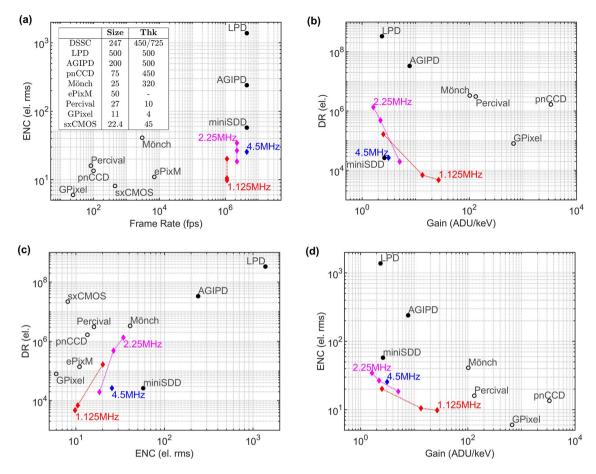

A summary of the CMOS-DEPFET ladder performance is presented in Fig. 10 together with the state-of-the-art detector systems aforementioned with the data available in literature<sup>2,4,12-17</sup>.

As can be seen in Fig. 10a, the ENC achieved with the prototype ladders is comparable to the soft X-ray detectors at all the operating frequencies. The outstanding noise figure of  $9.8~e^-$  rms is obtained at the peak frame rate of 1.125~MHz. The in-pixel electronics is capable to sustain a continuous MHz-frame rate with excellent noise performance. Compared to the detector in operation at EuXFEL, DSSC is placed in the unique position being able to cope with the XFEL bunch pattern at the ENC levels of the soft X-ray detectors.

**Figure 8.** Distribution (a) and map (b) of the equivalent noise charge.

**Figure 9.**  $^{55}$ Fe spectrum (a) obtained at 1.125 MHz showing the spectroscopic capabilities of the sensor at 18  $^{\circ}$ C and 300-ns integration time and increased flat-top time of 500 ns. (b) Zoom in the Mg peak region and a reference spectrum of a macro pixel from an early development stage sample of the CMOS-DEPFET fabrication measured at -50  $^{\circ}$ C and 3-μs shaping time (red curve).

| Frame rate (MHz) | t <sub>int</sub> (ns) | Filter C <sub>int</sub> (pF) | ADC coarse gain | Gain (ADU/keV) (%) | ENC (e <sup>-</sup> rms) | Dyn. range (ke <sup>-</sup> ) |

|------------------|-----------------------|------------------------------|-----------------|--------------------|--------------------------|-------------------------------|

| 4.5              | 30                    | 1                            | 1×              | 3.12 ± 3.65        | 25.5 ± 5.3               | 26                            |

| 2.25             | 50*                   | 1                            | 1×              | 5.05 ± 2.2         | 18.5 ± 2.7               | 19                            |

|                  |                       | 2.5                          | 1×              | 2.2 ± 4.4          | 26.6 ± 6.4               | 489                           |

|                  |                       | 3.4                          | 1×              | 1.63 ± 5.3         | 34.4 ± 9.5               | 1345                          |

| 1.125            | 300                   | 1                            | 2×              | 26.8 ± 2.5         | 9.8 ± 1.4                | 5                             |

|                  |                       | 1                            | 1×              | 13.4 ± 2.2         | 10.5 ± 2.1               | 7                             |

|                  |                       | 13.8                         | 1×              | 2.5 ± 5.5          | 20.14 ± 5.6              | 165                           |

**Table 1.** Summary of the results. \*The integration time for the 2.25 MHz operation was not maximized and can be increased, if needed, up to about 100 ns.

DSSC features generally a lower gain in contrast to all the detector alternatives. This is mainly associated to the lower ADC resolution and thus the need to adjust the detector sensitivity to the incident photon energy in order to maximize the performance. The CMOS-DEPFET first gain compression kink is at around 80 keV, and therefore the DR reaches the level of other soft X-ray detectors when the ASIC is operated at lower gains (Fig. 10b). Depending on the final user application, the single-photon resolution or the DR can be optimized (Fig. 10c). Lowering the photon energy, thus increasing the gain to achieve single photon resolution, lowers the achievable DR (Fig. 10d).

The DEPFET-equipped ladder showed its unique features and opens new possibilities in the X-ray imaging at megahertz frame rate. The front-end architecture together with the CMOS-DEPFET sensor proved to be an excellent base for further developments in the low-noise soft X-ray detectors at ultimate readout speeds. The DEPFET-dynamic range can be further tailored to the application by modifying the shape of non-linear response characteristics, e.g. moving the gain kinks to lower energies. Finally, the possibility to scale the pixel size, together with the usage of smaller technology node for the readout ASICs, will allow one to build higher spatial resolution cameras with megahertz readout speed, high dynamic range and ultimate single-photon sensitivity. With a proper power management, moreover, CW operation at higher bunch rates is also possible. This would make DEPFET and DSSC attractive for many facilities beyond the EuXFEL.

## Summary

Two DSSC ladder protoypes equipped with CMOS-DEPFET sensors were successfully operated and characterized. The first laboratory test campaign confirms the functionality of the electronics and readout ASIC, and shows the excellent performances achievable with the new sensors. The gain and noise figures have been experimentally evaluated, and a method to scan the non-linear response has been proposed. This allowed the estimation of the dynamic range. The protoypes were operated at different readout speeds to explore the capabilities of the system. The demonstrated performance fulfill the requirements at the EuXFEL soft X-ray instruments, and we started the series production to build the full camera.

**Figure 10.** Comparison of key figures for different detectors with respect to the CMOS-DEPFET detector (colored symbols). (a) Noise versus peak frame rate, together with an overview table on the pixel size and active thickness (Thk), both in  $\mu$ m. (b) Dynamic range versus gain, where gain data for ePixM and sxCMOS is not available. (c) Dynamic range versus Noise, and (d) Noise versus gain, where again the gain data for ePixM and sxCMOS is not available.

#### Data availability

The data presented in this study are available upon reasonable request to the corresponding author.

Received: 4 October 2022; Accepted: 11 July 2023 Published online: 21 July 2023

# References

- 1. Decking, W. et al. A MHz-repetition-rate hard X-ray free-electron laser driven by a superconducting linear accelerator. Nat. Photonics 14, 391–397. https://doi.org/10.1038/s41566-020-0607-z (2020).

- Veale, M. et al. Characterisation of the high dynamic range Large Pixel Detector (LPD) and its use at X-ray free electron laser sources. J. Instrum. 12, P12003. https://doi.org/10.1088/1748-0221/12/12/p12003 (2017).

- Galler, A. et al. Scientific instrument Femtosecond X-ray Experiments (FXE): Instrumentation and baseline experimental capabilities. J. Synchrotron Radiat. 26, 1432–1447. https://doi.org/10.1107/S1600577519006647 (2019).

- 4. Allahgholi, A. et al. Megapixels @ Megahertz—The AGIPD high-speed cameras for the European XFEL. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 942, 162324. https://doi.org/10.1016/j.nima.2019.06.065 (2019).

- 5. Wiedorn, M. O. et al. Megahertz serial crystallography. Nat. Commun. 9, 4025. https://doi.org/10.1038/s41467-018-06156-7 (2018).

- Madsen, A. et al. Materials imaging and dynamics (MID) instrument at the European X-ray free-electron laser facility. J. Synchrotron Radiat. 28, 637–649. https://doi.org/10.1107/S1600577521001302 (2021).

- 7. Porro, M. et al. The MiniSDD-based 1-Mpixel camera of the DSSC project for the European XFEL. IEEE Trans. Nucl. Sci. 68, 1334–1350. https://doi.org/10.1109/TNS.2021.3076602 (2021).

- 8. Hart, M. The large pixel detector for the European XFEL: Overview of the system and experience of operation at the FXE beam line. https://www.esrf.fr/files/live/sites/www/files/events/conferences/2018/IFDEPS/S7.02.Hart.pdf (2018).

- Büttner, F. et al. Observation of fluctuation-mediated picosecond nucleation of a topological phase. Nat. Mater. 20, 30–37. https://doi.org/10.1038/s41563-020-00807-1 (2021).

- Chattopadhyay, T. et al. First results on SiSeRO devices: A new X-ray detector for scientific instrumentation. J. Astron. Telesc. Instrum. Syst.https://doi.org/10.1117/1.JATIS.8.2.026006 (2022).

- 11. Lutz, G., Porro, M., Aschauer, S., Wölfel, S. & Strüder, L. The DEPFET sensor-amplifier structure: A method to beat 1/f noise and reach sub-electron noise in pixel detectors. Sensorshttps://doi.org/10.3390/s16050608 (2016).

- Bergamaschi, A. et al. The MÖNCH detector for soft X-ray, high-resolution, and energy resolved applications. Synchrotron Radiat. News 31, 11–15. https://doi.org/10.1080/08940886.2018.1528428 (2018).

- 13. Kuster, M. et al. The 1-megapixel pnCCD detector for the small quantum systems instrument at the European XFEL: System and operation aspects. J. Synchrotron Radiat. 28, 576–587. https://doi.org/10.1107/S1600577520015659 (2021).

- 14. Shike, H. *et al.* A global shutter wide dynamic range soft X-ray CMOS image sensor with backside-illuminated pinned photodiode, two-stage lateral overflow integration capacitor, and voltage domain memory bank. *IEEE Trans. Electron Devices* **68**, 2056–2063. https://doi.org/10.1109/TED.2021.3062576 (2021).

- Marras, A. et al. Characterization of the Percival detector with soft X-rays. J. Synchrotron Radiat. 28, 131–145. https://doi.org/10. 1107/S1600577520013958 (2021).

- Desjardins, K. et al. Backside-illuminated scientific CMOS detector for soft X-ray resonant scattering and ptychography. J. Synchrotron Radiat. 27, 1577–1589. https://doi.org/10.1107/S160057752001262X (2020).

- Rota, L. et al. Design of ePixM, a fully-depleted monolithic CMOS active pixel sensor for soft X-ray experiments at LCLS-II. J. Instrum. 14, C12014. https://doi.org/10.1088/1748-0221/14/12/c12014 (2019).

- Segal, J. et al. Thin-entrance window process for soft X-ray sensors. Front. Phys. 9, 618390. https://doi.org/10.3389/fphy.2021. 618390 (2021).

- Aschauer, S. et al. First results on DEPFET active pixel Sensors fabricated in a CMOS foundry—A promising approach for new detector development and scientific instrumentation. J. Instrum. 12, P11013. https://doi.org/10.1088/1748-0221/12/11/p11013 (2017).

- Andricek, L. et al. DePFET—Recent developments and future prospects. Front. Phys. 10, 896212. https://doi.org/10.3389/fphy. 2022.896212 (2022).

- Hansen, K. et al. Qualification and integration aspects of the DSSC mega-pixel X-ray imager. IEEE Trans. Nucl. Sci. 66, 1966–1975. https://doi.org/10.1109/TNS.2019.2927421 (2019).

- Hansen, K., Klär, H. & Müntefering, D. Camera head of the DSSC X-ray imager. In 2011 IEEE Nuclear Science Symposium Conference Record, 1713–1717. https://doi.org/10.1109/NSSMIC.2011.6154666 (2011).

- Kirchgessner, M. et al. The high performance readout chain for the DSSC 1Megapixel detector, designed for high throughput during pulsed operation mode. J. Instrum. 10, C01011. https://doi.org/10.1088/1748-0221/10/01/C01011 (2015).

- 24. Nidhi, S. et al. Safety-interlock system of the DSSC X-ray imager. In 2016 IEEE Nuclear Science Symposium, Medical Imaging Conference and Room-Temperature Semiconductor Detector Workshop (NSS/MIC/RTSD), 1-4. https://doi.org/10.1109/NSSMIC. 2016.8069824 (2016).

- Facchinetti, S. et al. Fast, low-noise, low-power electronics for the analog readout of non-linear DEPFET pixels. In 2011 IEEE

Nuclear Science Symposium Conference Record, 1846–1851. https://doi.org/10.1109/NSSMIC.2011.6154371 (2011).

- Hansen, K., Reckleben, C., Kalavakuru, P., Szymanski, J. & Diehl, I. 8-Bit 5-MS/s analog-to-digital converter for pixel-level integration. IEEE Trans. Nucl. Sci. 60, 3843–3851. https://doi.org/10.1109/TNS.2013.2280660 (2013).

- 27. Kemmer, J. et al. Experimental confirmation of a new semiconductor detector principle. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 288, 92–98. https://doi.org/10.1016/0168-9002(90)90470-Q (1990).

- 28. Schlee, S. A. Methods for the system calibration of the DSSC detector for the European XFEL. Ph.D. thesis. Staats-und Universitäts-bibliothek Hamburg Carl von Ossietzky (2018). https://ediss.sub.uni-hamburg.de/handle/ediss/7831.

- 29. Porro, M. Development of the DEPFET sensor with signal compression: A large format X-ray imager with mega-frame readout capability for the European XFEL. In 2011 IEEE Nuclear Science Symposium Conference Record, 1424–1434. https://doi.org/10.1109/NSSMIC.2011.6154343 (2011).

- Brinkmann, R., Schneidmiller, E., Sekutowicz, J. & Yurkov, M. Prospects for CW and LP operation of the European XFEL in hard X-ray regime. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 768, 20–25. https://doi.org/10.1016/j. nima.2014.09.039 (2014).

- Reckleben, C. et al. A 64-by-64 pixel-ADC matrix. In 2015 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), 1–4. https://doi.org/10.1109/NSSMIC.2015.7581817 (2015).

### Acknowledgements

The development described in this work was initiated and coordinated by the European XFEL (EuXFEL) GmbH, Schenefeld, Germany, in the framework of the DEPFET Sensor with Signal Compression (DSSC) Project. The implementation of the DSSC has been carried out by the DSSC consortium. Here the authors acknowledge all the present and former members of the consortium for their valuable contribution to the project. The authors thank A. Venzmer and E. Wüstenhagen, DESY, Hamburg, Germany, for the production, integration and testing of sub-assemblies and the preparation of the testing tools and setups. The publication is funded by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation)—491245950.

# **Author contributions**

S.M. and K.H. conceived the measurement campaign and wrote the manuscript. S.M. performed the measurements and data analysis. A.C. contributed to the measurement strategy and the data analysis. P.K. and C.R. contributed to the experimental setup optimization and designed the digitizer. S.A. and L.S. designed the CMOS-DEPFET and coordinated the production. C.F. coordinated the front-end design. K.H. coordinated the module design and contributed to the digitizer and system design. M.M. designed the injection and I/O circuitry and coordinated the bare module testing. F.E. designed the digital control circuitry, SRAM and global layout. P.F. coordinated the ASIC development and contributed to the system concept. H.K. contributed to the design of the printed circuit boards and of the testing tools. M.P. coordinated the DSSC project and contributed to the electronics readout and system concept. All authors reviewed the manuscript.

#### Funding

Open Access funding enabled and organized by Projekt DEAL. Funding was provided by Deutsche Forschungsgemeinschaft (German Research Foundation) (Grant No. 491245950).

### Competing interests

The authors declare no competing interests.

#### Additional information

**Correspondence** and requests for materials should be addressed to S.M.

**Reprints and permissions information** is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit <a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2023